Cadence 推出新一代音频应用设计 HiFi 5s 对称多处理器(SMP),专为解决生成式 AI 驱动的音频、沉浸式体验和先进车载娱乐系统等下一代音频解决方案的挑战而设计。新款 HiFi 5s 多核 DSP 提供 2 至 8 核心的可扩展性能,支持缓存一致性下的简化多核编程,并兼容 Zephyr 和 FreeRTOS 等可信平台。这将加速音频开发,显著简化软件设计与优化流程。

下一代消费电子和车载音频技术日益复杂,而诸如基于AI的生成式音频处理、沉浸式音景以及软件定义汽车的高级信息娱乐等市场驱动因素,都要求音频 DSP 性能的提升。然而,单个 DSP 已无法满足日益增长的计算需求,而多个 DSP 则带来了严峻的编程挑战。

如今,OEM 和 SoC 供应商必须独立完成所有多核硬件设计和软件开发,同时还要应对日益增长的上市时间压力。与此同时,程序员还面临着基于软件的共享内存区域同步以及在多核集群中合理划分任务的复杂性。这可能导致设计无法达到性能预期。

在这种快速发展的环境中,需要一种开箱即用的硬件设计和支持多核的操作软件,以缩短硬件设计时间并降低多核音频产品开发的软件复杂性。

为了简化多 DSP 的编程,Cadence 升级了其旗舰 Xtensa LX8 平台,使其具备对称多处理功能。全新 Xtensa Multicore LX8 平台允许 SoC 设计人员自动生成最多八个具有硬件缓存一致性的对称多处理器 (SMP) 集群。Cadence

将其性能最高、非常成功的 Tensilica HiFi 5s DSP 提升到新的高度,并推出了基于新平台的首款产品。Tensilica 缓存一致性 HiFi 5s SMP 提供可扩展的性能和更高的资源利用率,同时简化了各种音频 DSP 应用的软件开发。

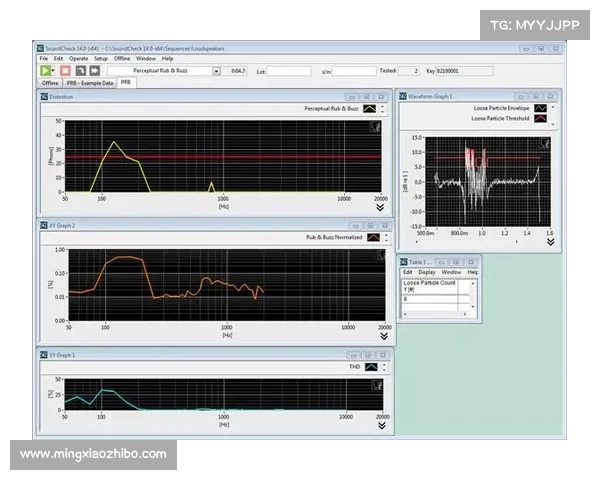

Tensilica 缓存一致性 HiFi 5s SMP 针对高性能、低功耗音频应用进行了优化设计,可从两核扩展到八核,并集成了中断分配器和跨核调试功能等集群功能。应用程序开发由两个流行的开源多核感知实时操作系统 (RTOS) Zephyr 和 FreeRTOS 支持。 Cadence 的 RTOS XOS 计划于 2025 年下半年推出多核支持。

在指定 HiFi 5s DSP 配置和内核数量后的几个小时内,开发人员即可从 Cadence 的 Xtensa 处理器生成器 (XPG) 下载多核集群,从而简化硬件集成。设计人员还将获得一个完整的、支持多核的软件开发工具包 (SDK)。

支持多核的 RTOS 会在各个内核之间分配任务,并管理跨内核软件同步,从而减轻应用程序的此类负担。缓存一致性使 SMP 集群中的每个内核都拥有统一的内存视图,从而避免了非一致性多核设计中经常出现的碎片化问题和利用率不足。这使得应用程序能够轻松地根据内核数量进行扩展,以支持不同的性能需求。

杜比实验室消费娱乐业务副总裁兼总经理 Mahesh Balakrishnan 表示:“从影院到家庭、手机,再到现在的汽车,享受杜比全景声 (Dolby Atmos) 体验从未如此轻松,我们能够为消费者带来创新的音频体验,这建立在与 Cadence 等合作伙伴的深度合作之上。我们非常高兴地庆祝这项最新创新,它将为 OEM 厂商提供更多选择,无缝满足日益增长的下一代音频需求。”

Cadence 的长期合作伙伴 DSP Concepts 的首席技术官 Paul Beckman 补充道:“我们很高兴看到 Cadence 市场领先的 Tensilica HiFi DSP 持续创新。我们备受赞誉的 Audio Weaver 工具生成的汽车和 TWS 音频应用程序可以高效地映射到 Tensilica Cache-Coherent HiFi 5s SMP,后者提供真正的并发处理能力,以实现可扩展的性能。凭借其硬件缓存一致性,我们可以避免基于软件的跨核同步的陷阱,使多核软件开发变得轻而易举。 ” “借助 AudioWeaver,OEM 厂商现在可以及时在 Cache-Coherent HiFi 5s SMP 上实现显著更高的性能配置,并确保最大限度地利用每个多核配置的总可用内存和周期。”

统一的资源视图简化了合作伙伴软件的上线流程,允许与客户代码共享可用的 DSP 周期和总可用内存。通过硬件管理缓存一致性,消除了跨核相关的软件同步错误,从而提高产品质量并减少退货。高度优化的 SMP 架构使音频应用能够实现与核心数量相匹配的接近理论最高性能。此外,它还极大地方便了对应用程序变化的适应,从而缩短了软件开发的整体完成时间。

Cadence 硅片解决方案事业部 Tensilica 产品市场高级总监 Chris Jones 解释道:“随着音频设备日益复杂化,管理复杂软件以及充分利用配备多个 DSP 的计算平台的潜力也面临挑战,易于编程和软件可靠性对于我们的客户获得竞争优势至关重要。我们全新的可配置 Tensilica 缓存一致性 HiFi 5s SMP 芯片,使客户能够高效扩展其音频产品,同时实现更高的资源利用率并加快产品上市时间。”

借助 Xtensa 平台一流的指令集可扩展性,开发人员可以增强 HiFi 5s ISA 指令集以优化其应用。Xtensa SDK 包含 SystemC 模型,有助于快速进行软件开发。企业可以从 Cadence 及其 200 多个强大的合作伙伴生态系统提供的大量 HiFi 优化软件包和音频/语音/语音编解码器中进行选择,从而快速为每个产品 SKU 提供合适的功能集。

缓存一致性 HiFi 5s SMP 现已上市,并已获得早期客户采用。开发人员可以通过 SDK 中提供的多核示例快速上手。